频率合成器(Frequency Synthesizer) 是通过合成方法产 生高精度、高稳定度时钟信号的电路。目前频率合成器的3种主要实现方法是直接频率合成、锁相(Phase Locked Loop,PLL)频率合成和直接数字顿率合成。

频率合成器(Frequency Synthesizer) 是通过合成方法产 生高精度、高稳定度时钟信号的电路。目前频率合成器的3种主要实现方法是直接频率合成、锁相(Phase Locked Loop,PLL)频率合成和直接数字顿率合成。锁相频率合成器是目前最常用的频率合成器,具有高集成度、低成本和高性能等特点。

频率合成器的主要性能指标如下。

(1)频率范围:输出的最低频率至最高频率的范围。

(2)频率精度:相邻两个输出频率之间的最小间隔。

(3)频率切换时间:从一个频率切换到另一个频率时,输出频率达到再次稳定时所需的时间。

(4)相位噪声:单位赫兹噪声功率谱密度与信号总功率之比的分贝值。

(5)杂散:输出频谱在某些频率点上出现的明显高于底噪的频率成分,其性能由载波与最大杂散成分的功率之比表征。

锁相频率合成器包括整数型(Integer-N) 频率合成器和分数型(Fractional-N)频率合成器。整数型频率合成器通过改变整数分频器的分频系数,使压控振荡器的输出频率是参考时钟频率的整数倍。分数型频率合成器通过动态改变分频比,使得分频比的平均值为分数,即输出频率是参考时钟频率的分数倍。

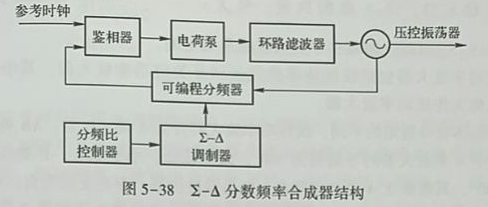

为了抑制分数频率合成器存在的分数杂散,采用 调制技术来实现噪声整形。

调制技术来实现噪声整形。 分数频率合成器成为目前研究的重点。典型的

分数频率合成器成为目前研究的重点。典型的 分数频率合成器

分数频率合成器

结构如图5-38所示,包括鉴相器、电荷泵、环路滤波器、压控振荡器、可编程分频器、调制器等功能模块。

随着集成电路技术的不断进步,新的技术与电路结构不断出现,进一步提升了频率合成器的性能,以及设计灵活性和工艺移植性,如使用数字电路实现的全数字锁相环(AII Digital Phase Locked Loop, ADPLL)、 倍频延迟锁相环(Multiplying Delay Locked Loop, MDLL)、 谐波注入锁定振荡器( lnjection-Locked Oscillator,ILO)、 基于亚采样鉴相器( Sub - Sampling Phase Detector,SSPD)的锁相环结构等。

今后,随着无线通信、雷达等技术的快速发展,高频率、大频率变化范围、低相噪、低功耗和高集成度已经成为频率合成器技术发展的方向。