可折叠硅集成电路是指具有可拉伸性、可折叠性的由硅材料制成的集成电路。此类器件在较大的力学形变情况下,如大幅度弯曲甚至折叠、横向拉伸、压缩、揉捏等,仍然能够很好地保持其电学性能并正常工作

可折叠硅集成电路是指具有可拉伸性、可折叠性的由硅材料制成的集成电路。此类器件在较大的力学形变情况下,如大幅度弯曲甚至折叠、横向拉伸、压缩、揉捏等,仍然能够很好地保持其电学性能并正常工作。其轻质、可折叠、可拉伸的性质将带来许多新的应用,由其直接集成的电子器件可应用在生物系统、医疗假肢和监测仪器等设备上。

长期以来,硅集成电路都是制作在刚性的不可弯折的硅硬衬底上的。近年来,随着以纳米级材料和结构为基础的柔性器件的发展,科学家们发现多数有机材料及某些无机电子材料在塑性或钢箔衬底上可以实现柔性,但无法拉伸或折叠。因此,采用硅材料、单晶硅阵列和柔性衬底,将多层中性机械平面布置(Multilayer Neutral Mechanical Plane Layouts)与集成电路中的逻辑门、振荡器、差分放大器等元器件相结合,研制出了高性能的单晶硅CMOS集成电路。

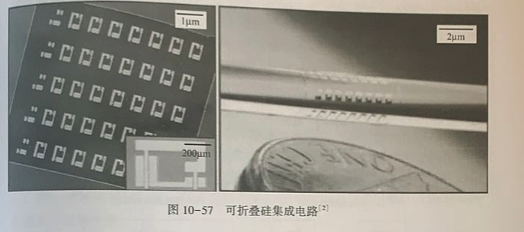

使用单晶硅的原因是它具有优良的电学性能,尤其是它还具有较高的载流子迁移率。研究人员将PMMA与聚酰亚胺(Polyimide, PI) 衬底旋涂到硅片上,通过转移(Transfer Printig)、离子刻蚀反应(Reactive Ion Etching)等技术可得到超薄的Si-CMOS/PI集成电路,并展现出较好的折叠性和伸展性,为柔性医学仪器的设计提供了新思路,如图10-57所示。

纳米级柔性电子学致力于提高电子器件的堆积密度,但采用纳米级别晶体管的柔性集成电路仍然是一个挑战。研究人员在超薄硅片上进行了纳米级别电路的集成,其中环形振荡器在0.9V电压下廷时仅有16ps。 通过剥落技术(SpalligTechnology),研究人员将超薄硅片转移到柔性衬底上,提高了器件的机械柔性。该研究采用主流硅处理技术,可以制备出高复杂度、低成本的超薄柔性集成电路。

可折叠硅集成电路有望在更多领域实现应用,包括监测并保障人体健康的可穿戴式系统,含有集成的电子器件的“智能”外科手套,含有焦平面阵列的半球村底电子眼型监测器等。