三维互连也称垂直互连或硅通孔(Through Silicon Via, TSV), 它是一种贯穿圆片或芯片(以下用圆片代表)整个厚度,实现圆片上、下表面的器件之间电学连接的互连器件。三维互连主要应用于三维集成结构中,实现圆片上表面器件与下表面器件或与相邻下层圆片的上表面器件之间的垂直电学互连。

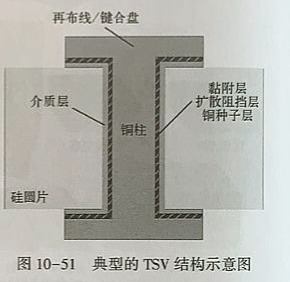

典型的TSV结构示意图如图10-51所示。由图可见,TSV 是由导体铜柱(一般是铜柱)、铜柱与硅圆片之间的介质层和黏附层/扩散阻挡层/铜种子层,以及铜柱两端的再布线/键合盘构成的。

根据不同的应用,TSV有多种制造方法。典型的铜导体柱TSV的制造方法如下:在完成集成电路制造后的圆片上,采用深反应离子刻蚀(DRIE)技术制造高深宽比的深孔;在深孔侧壁依次沉积介质层、黏附层、扩散阻挡层和铜种子层;利用电镀技术在深孔内填充导体铜柱;通过化学机械抛光平整化去除表面的过电镀铜层和铜种子层等,将圆片正面与一个辅助圆片进行临时键合;从圆片背面减薄,使铜柱底部露出,再利用干法刻蚀对圆片背面进行回刻,使铜柱末端凸出于圆片背面;在回刻后的背面沉积介质层,并通过化学机械抛光去除铜柱顶端覆盖的介质层,使其曝露出来,完成TSV的整个制造过程。

在芯片的最小厚度受到机械强度、可制造性和散热等因素的限制下,为了减小TSV占用的芯片面积,需要TSV具有较高的深宽比。一般TSV的深宽比大于5:1甚至超过10:1。制造高深宽比TSV的主要难点是,在高深宽比深孔内部沉积厚度均匀的介质层、黏附层、打散阻挡层和铜种子层。介质层一般为SiO2,通常采用等离子体增强化学气相沉积(PECVD) 或常压化学气相沉积(APCVD)制造,APCVD具有更好的共形沉积能力,能够在10:1的深孔内壁沉积厚度均匀的SiO2介质层。黏附层、扩散阻挡层和铜种子层的材料通常借用平面铜互连的材料体系,如Ti/TiW/Cu等。

在量产应用中,考虑到生产效率,在深宽比深孔内壁沉积上述薄层金属的常用方法是离子化物理气相沉积技术,这种技术能够在10:1的深孔侧壁沉积连续、均匀的金属层。铜柱填充采用铜电镀技术。为了避免在高深宽比深孔内部电镀时容易出现的封口效应而导致铜柱内部形成残留的镀液或空洞等缺陷,电镀液中需要添加较为复杂的添加剂,包括加速剂、抑制剂和平整剂。这些添加剂能够在提高深孔底部电镀速度的同时,抑制深孔开口位置和圆片表面的铜电镀速度。另外,电镀时采用脉冲反向电镀波形,通过反向脉冲周期的电化学反应,可消除正向电镀周期内开口位置电镀