铁电随机存取存储器(Ferroelectric Random Access Memory, FeRAM),简称铁电存储器,是一种基于“可编程铁电电容”的存储技术。

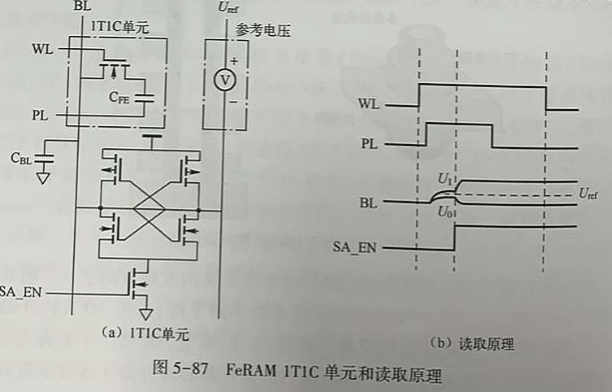

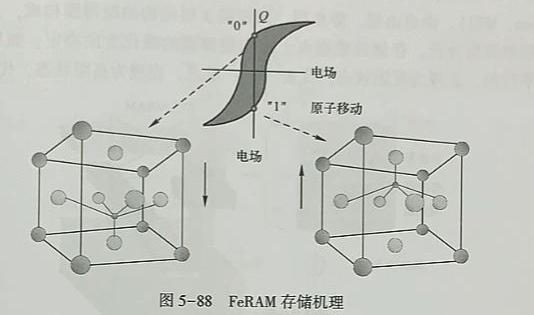

铁电随机存取存储器(Ferroelectric Random Access Memory, FeRAM),简称铁电存储器,是一种基于“可编程铁电电容”的存储技术。FeRAM 通常采用1TIC结构,如图5-87 (a)所示,但铁电电容器与一般电容器不同,它的两个电极板中间沉淀了一层晶态的铁电晶体薄膜,通过铁电晶体中心原子位置的不同表示数据。如图5-88所示,当一个电场被施加到铁电晶体上时,中心原子在电场的作用下运动;而当电场从晶体上移走后,中心原子会保持在原来的位置而处于一个稳定极化状态。读操作过程是在存储单元电容器上施加一已知电场,如果晶体的中心原子原来的位置与所施加的电场方向使其要达到的位置相同时,则中心原子不会移动。若相反,则中心原子将越过晶体中间层的高能阶到达另一位置,翻转成另一稳定极化状态,导致充电波形上出现一个脉冲,即产生原子移动的比没有产生原子移动的多了一个脉冲;把这个充电波形同参考电压进行比较,便可以检测出存储单元中的内容。

由于读操作会导致存储单元状态的改变,所以利用铁电薄膜电容效应的存储器是破坏性读出(Destructive Read Out,DRO) FeRAM,每个读操作后需要电路自动恢复数据。读取通常采用电压利灵敏放大器(Voltage Mode SA, VSA),其读取原理如图5-87 (b)所示。 读取时,首先BL被预充到0,然后激活WL至UDD+UTH (UTH为场效应管的阈值电压),基板线( Plate Line, PL)施加电压UDD。当存储数据为0时,CFE=C0,BL电压变为U0=UDD[C0/(C0+CBL)];当存储数据为1时,CFE=C1, BL电压变为U1=UDD[C1/(C1+CBL)],最后使能SA,与参考电位Uref=(U0+U1)/2进行比较最终读出数据。WL电压保持至灵敏放大后的位线电压回写到存储单元后再撤销。

还有一种非破坏性读出(Non-destuctive Read Out, NDRO)的FeRAM。NDRO FeRAM也是利用铁电薄膜的极化特性,以铁电薄膜取代常规MOS场效应管中的栅介质层而构成的铁电介质栅极场效应管(Metal-Ferroeletric-Semiconductor FET, MFSFET)作为存储单元。利用铁电薄膜的极化状态调制半导体表面状态,从而调制晶体管源极和漏极之间的导通状态来区别“0”和“1”。读取时铁电薄膜的极化状态不会改变,所以存储状态也不会改变。