为了提高无线移动通信芯片的集成度,降低成本,快速发展的Si CMOS工艺已经成为无线通信芯片的主流工艺;同时,这也对传统的射频集成电路(Radio Frequency Inegrated Circuit, RFIC) 设计方法提出了新的挑战。

为了提高无线移动通信芯片的集成度,降低成本,快速发展的Si CMOS工艺已经成为无线通信芯片的主流工艺;同时,这也对传统的射频集成电路(Radio Frequency Inegrated Circuit, RFIC) 设计方法提出了新的挑战。2000年以后提出了使用局部数字化方法或完全数字化方法实现连续时间的射频和模拟功能,即数字射频集成电路(Digital RF Intergrated Gircuit)技术。

自数字射频技术提出以来,关于射频收发机能否完全数字化的论题,一直是引入关注的热点。在当前的Si CMOS工艺条件下,受系统线性度、功耗和抑制干扰能力等因素的制约,通过数字辅助技术,可以增强射频模拟电路的性能,但还无法被数字电路完全取代,如射频接收机的前端低噪声放大器、片外的带通滤波器、功率放大器等。

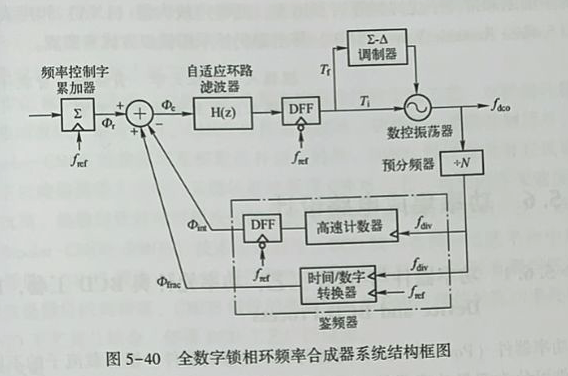

频率合成器则是一个基 本实现了全数字化的射频集成电路功能模块。全数字锁相环( All Digital Phase Locked Loop, ADPLL) 频率合成器的系统结构框图如图5-40所示,包括数控振荡器、鉴频器、环路滤波器和频率控制电路等。数控振荡器产生系统所需的高频信号,其功能与传统频率合成器中的压控振荡器类似。鉴频器主要由时间数字转换器和高速计数器组成,其输出与频率控制字进行比较,通过环路滤波等处理后,产生数控振荡器的控制字。整个系统形成负反馈,使得数控振荡器输出稳定的频率。

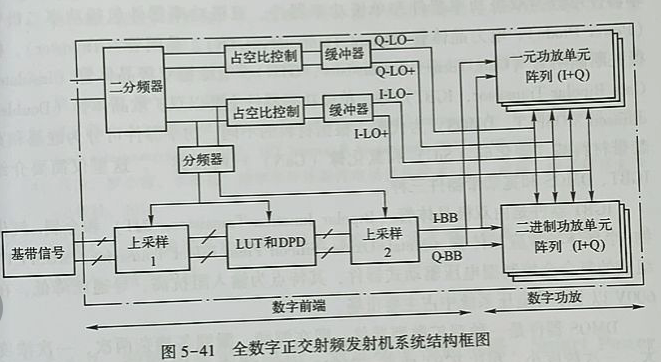

一个适用于宽带无线通信的全数字正交发射机的系统结构框图如图5-41所示,前端基带电路和功率放大器均采用数字化设计。为了抑制远离载波频率的噪声和重复频谐,数字基带信号通过两次上采样(Up Sampling)调制到一定的频段上;查找表(Look-Up Table, LUT) 和数字预失真( Digial Predisortion, DPD)用来重塑后级数字功率放大器的线性度。

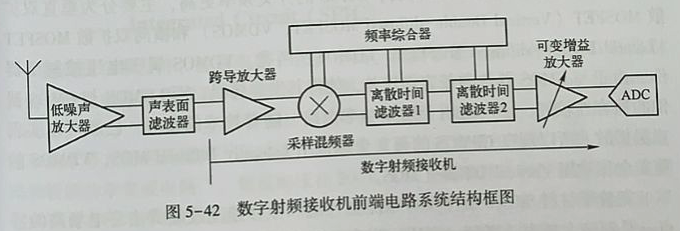

一个适用于WiMAX (Worldwide Interoperability for Microwave Access)的数字射频接收机前端电路系统结构图如图5-42所示,它包括跨导放大器(Gm Amp)、采样混频器(Sampling Mixer)和两级开关电容离散时间滤波器等模块。从噪声抑制和带外干扰抑制等因素出发,低噪声放大器(LNA)和声表面滤涉器(Surface Acoustic Wave, SAW)等电路仍然采用模拟方式来实现。