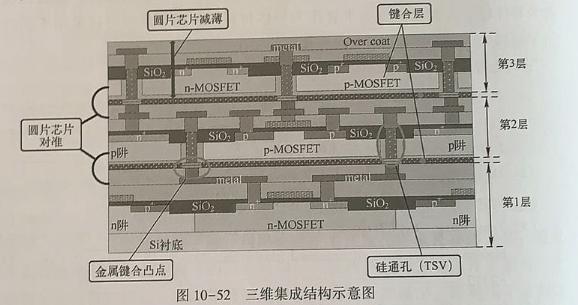

三维集成是指将多层集成电路在垂直方向上堆叠集成为一体使其如同单一器件,并利用垂直互连(也称三维互连或硅通孔)实现相邻两层之间的电信号连接,从而利用第3个维度的集成提高系统的性能,降低功耗,减小面积并实现异质集成,如图10-52所示。三维集成的研究工作始于20世纪80年代末期,日本东北大学、德国Fraunhofer IZM 研究所、比利时微电子研究中心(IMEC)、美国伦斯勒理工学院和IBM等,先后投入力量对不同的三维集成制造方案进行研究,并在21世纪初吸引了广泛的关注。在学术界和工业界的共同努力下,三维集成技术得到了快速发展,并在多种工业产品中得到广泛应用。

以TSV为基础的的三维集成需要TSV制造、圆片减薄和圆片键合等额外的制造技术。典型的三维集成制造过程如下所述。

(1)从圆片正面向圆片内刻蚀高深宽比的深孔。

(2)在深孔内壁沉积绝缘介质层、黏附层、扩散阻挡层和铜种子层。

(3)在深孔内电镀填充金属铜,形成导体柱。

(4)在圆片正面制造再布线和金属键合凸点,并在圆片正面临时键合辅助圆片。

(5)利用机械研磨和化学机械抛光等减薄圆片背面,使导体柱曝露出来。

(6)在圆片背面制造介质层、平面互连和金属键合凸点。

(7)将圆片与另一个圆片进行对准与永久键合,然后去除辅助片,实现双层圆片的三维集成。

需要说明的是,不同的实现方案可能采用不同的工艺顺序,这会导致三维集成的主要制造过程有一定的变化。

根据TSV制造顺序所对应的集成电路前道工序(FEOL)和后道工序(BEOL)的不同,可以将三维集成的制造方法分为Via First、 Via Middle和Via Last三种。Via First方案是在制造晶体管前首先制造TSV; Via Middle方案是在晶体管制造完成后制造TSV,然后制造平面金属互连; Via Last方案是在晶体管和平面互连全部完成后再制造TSV。这三种技术方案有各自的优缺点和不同的适用范围。例如,Via Middle技术可以实现更小直径的TSV,但是只适合独立的制造商或代工厂采用;而Via Last 方案可以被封装厂采用,但是制造的TSV直径较大。

三维集成的主要优点包括如下5个方面。

(1)降低互连总长度:三维集成可以缩短总互连长度,从而提高性能,减少中继器,降低功耗。

(2)提高数据传输带宽:采用高密度TSV可以提高数据传输带宽。例如,三星公司的4GB DRAM芯片HBM2,采用4层8Gb存储器芯片和1层缓存芯片,每层存储器芯片超过5000个TSV,能够实现256GB/s的数据传输率,是GDDR5的7倍。

(3)减小芯片面积:高度方向的多层集成可以大幅度降低芯片面积。例如,AMD公司的HBM ( High-Bandwith-Memory)在带宽提高60%、功耗降低50%的情况下,芯片占用的PCB面积比GDDR5减小94%。

(4)提高集成度:三维集成不依赖于集成电路特征尺寸,可以适用于任何工艺节点,因此利用第3维可以线性提高集成度,从而在不继续减小特征尺寸的情况下,仍旧保持集成度继续增长。例如,三维集成使NAND闪存的容量得到提升,维持了摩尔定律的发展速度。

(5)实现异质芯片集成:三维集成的多层芯片可以是不同工艺甚至不同衬底的芯片,从而能够实现RF、光电子、MEMS、 传感器等与CMOS的三维集成。

三维集成突出的优点使其具有十分广阔的应用前景。2008 年,东芝公司首先量产了基于TSV的CMOS图像传感器,随后三维集成的MEMS及传感器、存储器、FPGA、 功率器件、射频与无线、逻辑与存储集成等产品相继投人量产。随着产业链的持续发展,三维集成制造技术将进一步发展, 成本也将逐渐降低,进而使其获得更加广泛的应用,促进多功能、高性能、小体积、低功耗的系统级集成芯片的发展。