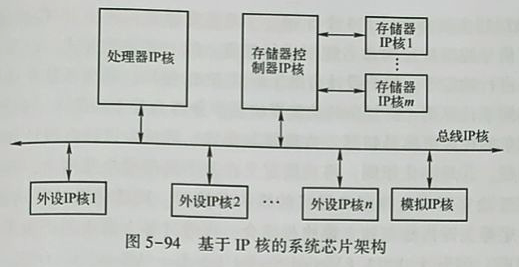

IP核(Intellectual Property Core)是指应用于系统芯片中包含特定功能可被复用的电路模块,它具有标准化和可交易等特点。IP核通常是已通过了产业化验证的成熟电路模块,可被系统芯片设计人员直接集成入芯片,能显著缩短设计研发的周期。由于很多设计技术集中体现在IP核中,特别是IP核设计者的知识产权,使得IP核具备了知识产权载体的作用。这也是为什么使用知识产权的缩写IP来表示这种电路模块的原因。在现代系统芯片设计方法中,设计人员能够以IP核为基础,进行包含数字/模拟集成电路核现场可编程逻辑门阵列等模块的系统芯片设计。一个基于IP核的系统芯片架构如图5-94所示。

从提交形式上看,IP核分为软核(Soft Core),硬核(Hard Core)和固核(Firm Core)3种。软核是与工艺无关的寄存器传输级(RTL)硬件描述语言(HDL)描述的设计代码。软核是基于IP核功能的描述,并且经过行为级设计优化核功能验证,可灵活应用于各种工艺。硬核是软核通过逻辑综合,布局布线之后的物理实现版图,形式是电路物理结构掩模版图核应用时所需的全套工艺文件。硬核的优点是电路布局布线与具体工艺绑定,可以确保性能,功耗等要求,并缩短系统芯片的设计时间;缺点是其灵活性较差,工艺跃迁难。固核的形式处于软核和硬核之间,固核一般以网表的形式提交。固核一般有用户来完成最终的布局布线,因此核的形状,大小以及核的端口位置都可改变因此与硬核方式相比它具有更大的灵活性。

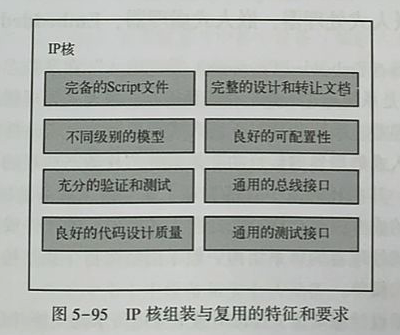

IP核复用是系统芯片提升设计效率的有效手段。为了让IP核能够在不同的系统中复用,关键是要将IP核进行组装。IP核组装与复用的特征和要求如图5-95所示。IP核组装需要从不同方面描述IP核的完整信息,包括配置文件,信号端口定义,总线类型和寄存器地址分配等。为确保IP核的复用性,IP核组装需要考虑核检查IP核所产生的各种信息是否满足复用标准,与EDA工具,软硬件库和硬件设计平台之间的兼容性,并评估IP核的质量与可复用等级。

IP核组装主要遵循以下3个原则。1规范化原则:统一IP核的设计规范,如对接口信号按照特定的命名规则进行规范;统一复位的方式,以及对编写代码的风格进行约定等。规范设计有助于后续IP的使用,减少系统集成时的引入错误。2简单化原则:将复杂的功能模块逐步分解为若干功能单一的特定模块。通常,简单的设计更容易被第三方理解与集成,可减少设计者设计和验证阶段引入的问题。3局部化原则:将功能定义在若干局部模块范围内,各局模块的功能相互独立正交,并定义显示的模块间接口。局部化设计将功能,成本,功耗和时序等关键指标与独立模块相结合,再通过各个模块的拼接形成复杂的IP核。