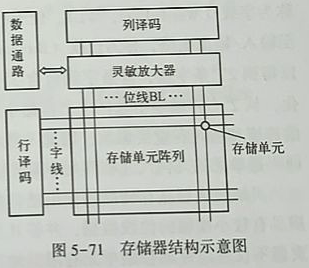

存储器包括存储单元、行译码器、列译码器和灵敏放大器等,如图5-71所示。

存储单元是存储器最基本的存储器件,可以用来存储一位或多位二进制信息“0”或“1”,具有存储数据和读/写数据的功能。例如,经典的6T结构静态随机存取存储器(SRAM)的存储单元由6个场效应管组成,利用内部反馈保持数据。动态随机存取存储器( DRAM)的存储单元为1TIC (1个场效应管、1个电容器)结构,利用存储单元中的电容器有无电荷来表示状态“0”和“1”。闪存(Flash)的存储单元为浮栅场效应管,利用场效应管的阈值高低不同表示不同的状态。

若干存储单元以某种组织结构组成存储阵列。例如,一个存储阵列包括2(P)个存储块,每个存储块包括2(n)个存储字(存储字为从存储阵列同时写入或读出的某一位宽的数据),每个存储字位宽为2(m),p代表块地址的位数,n 代表每个存储块中行和列地址位数,列地址为A0~Ak-1,行地址为Ak~An-1,所以存储器的容量为2(p+n+m)位。存储器采用较长的字线和位线可以实现大容量,但是长位线、字线上的寄生电容和电阻又会导致存储器速度下降,因此设计需要对存储器阵列的组织和划分进行优化,使各个存储块的字线和位线长度保持在一定的界限内,以达到速度、容量的平衡。

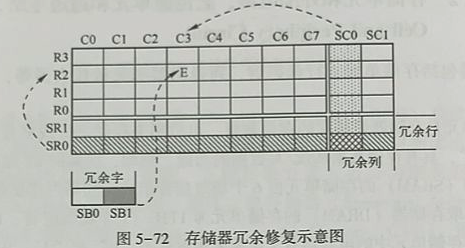

为保证成品率,存储器在正常的存储阵列之外通常还会增加额外的冗余存储阵列。当存储阵列出现故障时,可以使用冗余存储阵列中的冗余行、冗余列或者冗余字进行替换修复。如图5-72所示,冗余存储单元阵列包含两个冗余行(SRO, SR1)、两个冗余列(SCO, SCI) 和两个冗余字(SBO, SB1)。 当位于R2行C3列的存储字E出现错误时,可以使用冗余行SRO直接替换R2行,或者可以使用冗余列SC0替换C3列,也可以直接使用冗余字SB1对E进行替换。一般冗余行和冗余列用于修复局部故障行和故障列,冗余字用于修复单个单元故障。冗余存储阵列的容量随正常存储阵列容量的增大而增加。存储器设计过程中需要根据存储器阵列故障类型和概率,分析最小存储块中所需要的冗余阵列中的容量和大小,以达到使用最少的冗余单元极大地提高成品率的目的。

行译码器将行地址线转化为行选择线,每一条行选择线可以选择行单元,称为字线( Word-Line, WL)。位于不同行但同一列的单元经由共同的连接线连至输入/输出电路,称为位线(Bit-Line, BL)。 行地址Ak~An-1 经过行译码器可以得到2一条字线,每条字线包含2(k)个存储字,列译码器对k位列地址进行转化,从2(k)个存储字中选择1个存储字进行操作。行译码器和列译码器对存储器的速度和功耗有重要影响,因此一般都将其紧密地搭接到存储器阵列,并保证译码器单元的几何尺寸和阵列节距尺寸匹配。

灵敏放大器是存储器读出电路的核心。它本质上是一个模拟电路。通过分辨具有较小摆幅的位线数据,并将其放大成具有较大输出摆幅的信号,灵敏放大器不仅可以弥补存储单元有限的输出驱动能力,减小延时,而且可以减少读出时位线上的信号摆幅,大大减少与充放电相关的功耗。灵敏放大器的拓扑结构在很大程度上取决于存储单元的类型、电压大小及存储器的整体结构。常用的灵敏放大器是差分电压灵敏放大器。

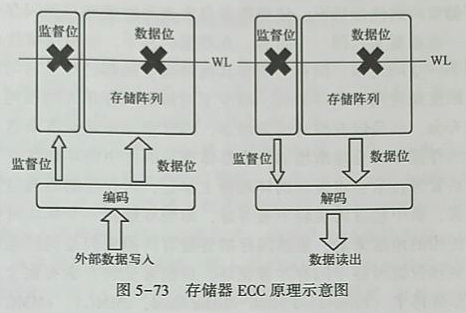

纠错编码(Error Correction Coding, ECC) 广泛应用于存储器及其控制器中,它能发现存储数据的错误并纠正这些错误从而提高存储器的可靠性。存储器ECC原理如图5-73所示。为了支持ECC,存储器在设计时需要增加额外存储阵列以保存监督位数据。有的存储器在设计时已经内嵌必要的ECC编解码电路,因此可以实现自检测修复。例如,具有内嵌ECC的DRAM既有更高的可靠性和成品率,又与标准的DRAM接口兼容。有的存储器只有存储数据位和监督位,ECC编解码由存储器控制器完成。例如,一般闪存中会给ECC监督位预留存储空间,若与支持ECC功能的闪存控制器配合使用,将显著提高其使用寿命。