动态随机存取存储器(Dynamic Random Access Memory, DRAM)依靠存储在电容上的电荷来保持信息。由于场效应管漏电的存在,电荷不能长期保存,故需要周期性地刷新以保持存储内容不丢失。

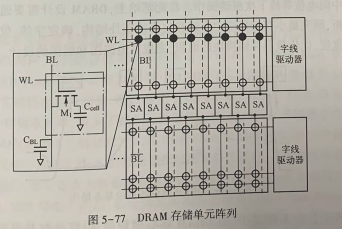

常见的DRAM存储单元由1个场效应管和1个电容(1T1C)构成,如图5-77所示。写入时,字线WL有效,场效应管导通:若写“1”,存储电容被充电;若写“0",存储电容被放电。读出时,位线BL首先预充,然后当字线有效时,位线寄生电容CBL和存储电容Ccell之间发生电荷重新分配,这就使位线上的电压发生变化。这一变化的方向决定了被存放数据的值:若位线电压变化为正值,则读出数据为"1”,反之则读出数据为“0"。由于存储电容通常要比位线寄生电容小一至两个数量级,这一电压变化极小, 一般在200mV左右。增大存储电容对增加位线电压摆幅和存储内容保持时间以及减少软错误十分必要,但与提高存储密度相矛盾。

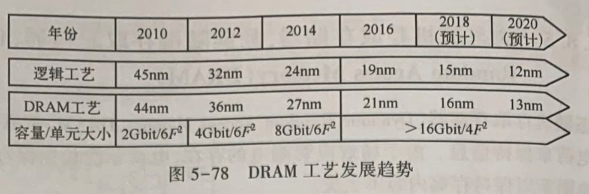

为了实现较高的存储单元密度和较低的每位成本,DRAM工艺在不断微缩;同时为了保持存储单元的性能,DRAM需要专门的制造工艺。目前常用的堆叠电容(Stacked Capacitor)工艺将电容堆叠在存取管和位线的顶部,应用多层材料堆叠实现大的电容。另外,还用沟槽电容(Trench Capacitor)工艺在衬底中刻蚀出沟槽,将其侧壁和硅片衬底作为电容的电极。通过将单元延伸为三维结构,单个DRAM存储单元的面积达到6F2(F为工艺特征尺寸)。DRAM工艺发展趋势如图5-78所示。

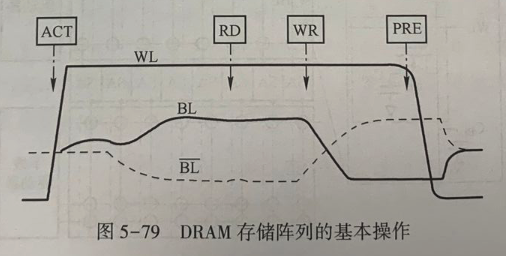

DRAM的核心模块由存储单元阵列、灵敏放大器(SA)和字线驱动器构成,其性能和面积是整个DRAM芯片性价比的基础。在存储单元阵列中同一行的存储单元共享一个字线,同一列的存储单元共享一个位线。 DRAM存储阵列的基本操作如图5-79所示,灵敏放大器采用差分结构,其输入是互补的位线BL和BL,负责在读数据时将位线上的微小电压差放大,在写数据时对存储单元进行回写。字线驱动器控制字线的开关。DRAM核心模块支持激活( ACT)、写(WR)、读(RD)和预充(PRE)4个基本操作。1 个字线连接的所有存储单元,称为1页(Page),会同时被激活。在字线为高时,由于存储单元电荷和位线电荷的再分配,如果存储单元保存的高电平,则与之相连接的位线电压会略有上升。

此时,存储单元中存储的数据由于电荷损失已经丢失,等待位线上电压差稳定后,灵敏放大器开始工作,将位线上的电压差放大至全摆幅并保持。由于字线仍然打开,此时灵敏放大器通过位线完成了存储单元的回写又恢复了其原有数据,这个过程称为刷新。激活操作完成后,该页上的数据可以进行随机读写。根据列地址,读操作将相应列灵敏放大器的数据读出;写操作将数据写入灵敏放大器再由灵敏放大器将数据回写至存储单元。预充操作将激活的页关闭,包括关闭字线,关闭灵敏放大器并将位线预充至中间电位等待下次激活操作。在此基础上,DRAM设计需要通过仿真和可靠性分析,研究最小存储模块中字线和位线的拓扑结构,确定字线、位线和数据线的物理宽度,优化最小存储模块的面积,完成其电路图和版图的设计。

虽然工艺在不断进步,但DRAM核心模块的读/写速度并没有显著提升。DRAM通过提高内部并行度的预取技术以及高速数据通路和高速接口技术来提升存取速度,并由此衍生出一系列的产品:SDRAM(同步动态随机存取存储器)、DDR DRAM(双倍速率同步动态随机存取存储器)、DDR2 DRAM(第二代双倍速率同步动态随机存取存储器)、DDR3 DRAM(第三代双倍速率同步动态随机存取存储器)和DDR4 DRAM(第四代双倍速率同步动态随机存取存储器)。