静态随机存取存储器(Static Random Access Memory ,SRAM)采用具有内部反馈的存储单元保存数据。相比DRAM,它存取速度快,并且只要不断电,数据可以一直保存 ,不需要刷新,缺点是存储单元复杂、容量低。

静态随机存取存储器(Static Random Access Memory ,SRAM)采用具有内部反馈的存储单元保存数据。相比DRAM,它存取速度快,并且只要不断电,数据可以一直保存 ,不需要刷新,缺点是存储单元复杂、容量低。

SRAM根据接口可分为异步SRAM和同步SRAM。异步SRAM的访问独立于时钟,数据输入和输出都由地址的变化控制。同步SRAM的所有访问都在时钟的上升沿/下降沿启动,地址、数据输入和其他控制信号均与时钟信号相关。SRAM又有分立式和嵌入式两种不同的应用方式。分立式SRAM作为独立元件主要用于通信设备、高速网络设备等领域。嵌入式SRAM由于与标准的CMOS工艺兼容,在SoC设计中获得了广泛的应用,如高速缓存、寄存器堆、查找表等,具有省面积小、速度快、功耗低的优点。嵌入式SRAM通常以编译器的形式出现,可根据用户自定义的位宽、字深等参数实时生成版图、网表和时序模型等文件。

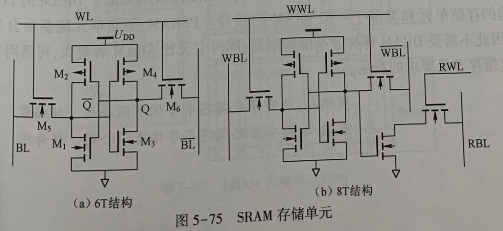

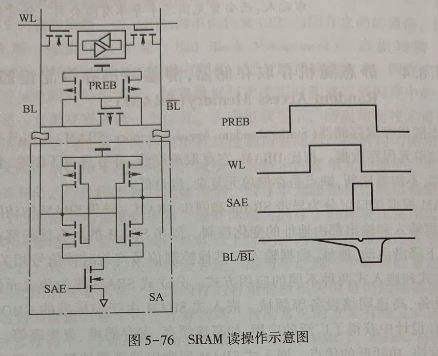

SRAM存储单元有6T结构、8T结构等多种形式,如图5-75所示。最常用的6T结构的SRAM存储单元包含一对交叉耦合的反相器(用来保持数据)和一对存取管(用来读出和写入)。写入时,升高字线WL,写入数据通过一对互补的位线BL和BL克服交叉耦合反相器的作用将数据写入节点Q,其非值写入节点Q。SRAM读操作示意图如图5-76所示。读出时,先将两条位线BL和BL预充电至高电平,然后预充电信号PREB升高将位线浮空。当字线WL上升时,位线BL和BL之间逐渐出现电压差,当电压差达到一定值后打开灵敏放大器(SA) ,对电压差进行放大,读出数据再送到输出电路。

SRAM存储单元设计是SRAM设计的主要挑战之一 。在尽量减小单元尺寸的同时,既要满足可读性的约束,又要满足可写性的约束,即交叉耦合反相器既要足够强不会在读期间被干扰而翻转,又要足够弱,能在写期间被克服。通常SRAM存储单元已不再由设计者开发,而由工艺厂提供,并针对具体的制造工艺进行了精心调制,可有多种不同速度功耗特点的种类供选择。

伪静态随机存取存储器( Pseudo SRAM,PSRAM )采用类似于DRAM的1T+1C结构的存储单元和类似于一般SRAM的接口。PSRAM存储单元刷新由自身完成,因此不需要DRAM那样复杂的控制器;同时它又比SRAM容量大,可适用于有一定缓存容量要求的产品。